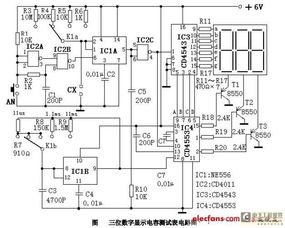

三位數(shù)字顯示電容測試表電路設(shè)計詳解

三位數(shù)字顯示電容測試表是一種用于精確測量電容值的電子儀器,其核心在于將待測電容的容量值轉(zhuǎn)換為可被數(shù)字電路處理和顯示的標準信號。本文將圍繞其系統(tǒng)架構(gòu)、關(guān)鍵集成電路設(shè)計以及工作流程進行詳細闡述。

一、 系統(tǒng)總體架構(gòu)

該電容測試表通常由以下幾個核心模塊構(gòu)成:

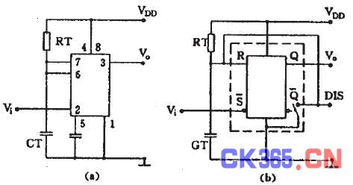

- 電容-頻率/時間轉(zhuǎn)換電路:這是測量的核心。常見方案是利用待測電容(Cx)構(gòu)成振蕩器(如555定時器構(gòu)成的多諧振蕩器)或單穩(wěn)態(tài)觸發(fā)器。電容值的變化直接改變輸出脈沖的頻率或?qū)挾取@纾趩畏€(wěn)態(tài)模式下,輸出脈沖的寬度 T = k R Cx(k為常數(shù),R為基準電阻),從而將電容值轉(zhuǎn)換為時間信號。

- 時基與控制邏輯電路:產(chǎn)生精確的閘門時間(如100ms),用于控制對轉(zhuǎn)換后脈沖信號的計數(shù)時間。此部分通常由晶體振蕩器、分頻器及邏輯門電路構(gòu)成,確保測量周期的準確性。

- 計數(shù)與鎖存電路:在閘門時間內(nèi),對電容-頻率轉(zhuǎn)換電路輸出的脈沖進行計數(shù)。計數(shù)結(jié)果即與電容值成正比。該數(shù)據(jù)被鎖存以保持顯示穩(wěn)定。此功能可由計數(shù)器集成電路(如CD4553三位BCD計數(shù)器)完成。

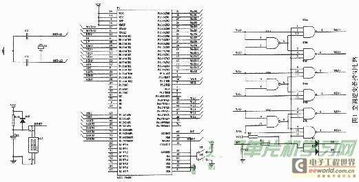

- 顯示驅(qū)動與譯碼電路:將計數(shù)器輸出的BCD碼轉(zhuǎn)換為七段數(shù)碼管所需的驅(qū)動信號。常用集成電路如CD4511 BCD-七段鎖存/譯碼/驅(qū)動器。

- 顯示單元:三位七段數(shù)碼管,用于直觀顯示電容值,單位通常為pF、nF或μF,可通過量程切換電路指示。

二、 關(guān)鍵集成電路設(shè)計與選型

- 電容-電壓/時間轉(zhuǎn)換IC:

- 方案A(基于555):采用NE555定時器構(gòu)成單穩(wěn)態(tài)電路。設(shè)計時,基準電阻Rref需選用高精度、低溫漂的金屬膜電阻。輸出脈寬 T ≈ 1.1 Rref Cx。該電路簡單,但線性度和精度受555自身性能限制,適用于中低精度測量。

- 方案B(專用電容測量IC):如TLC555的改進型或?qū)S玫碾娙?數(shù)字轉(zhuǎn)換芯片(如AD7745)。后者集成度更高,采用Σ-Δ轉(zhuǎn)換技術(shù),直接輸出數(shù)字信號,精度和抗干擾能力顯著提升,但成本較高。

- 計數(shù)器/邏輯控制IC:

- 核心芯片:CD4553是一款經(jīng)典的三位BCD計數(shù)器,內(nèi)部包含三個負沿觸發(fā)的BCD計數(shù)器,并有多路掃描輸出,可高效驅(qū)動三位數(shù)碼管。其時鐘輸入(CLK)接收來自轉(zhuǎn)換電路的脈沖,計數(shù)使能(DIS)由閘門時間信號控制,鎖存(LE)和復位(MR)信號由時基控制邏輯生成。

- 譯碼驅(qū)動與顯示IC:

- CD4511接收CD4553輸出的BCD碼,并將其譯碼后驅(qū)動共陰極七段數(shù)碼管。它內(nèi)部集成鎖存器,可與CD4553的鎖存信號配合,消除顯示閃爍。

- 時基產(chǎn)生IC:

- 可采用晶體振蕩器配合14級二進制分頻器CD4060產(chǎn)生穩(wěn)定的基準頻率,再經(jīng)后續(xù)分頻得到所需的閘門時間(如由32768Hz晶振經(jīng)分頻得到2Hz信號,其半周期即為250ms的閘門時間)。

三、 工作流程與設(shè)計要點

- 測量周期:系統(tǒng)以固定周期工作。控制邏輯發(fā)出復位信號,清零計數(shù)器。開啟精確的閘門時間(例如100ms),在此期間,由Cx決定的脈沖被送入計數(shù)器計數(shù)。閘門時間結(jié)束時,控制邏輯發(fā)出鎖存信號,將計數(shù)值鎖存至譯碼驅(qū)動器,并更新顯示。之后,系統(tǒng)復位,準備下一次測量。

- 量程切換:為覆蓋更寬的測量范圍(如幾pF到幾百μF),需設(shè)計量程切換電路。可通過繼電器或模擬開關(guān)切換不同阻值的基準電阻(Rref),或改變閘門時間,同時調(diào)整小數(shù)點顯示位置。量程切換可由手動開關(guān)或自動量程轉(zhuǎn)換邏輯實現(xiàn)。

- 校準與精度保障:

- 校準:使用高精度標準電容在特定量程進行校準,通過調(diào)整基準電阻或時基參數(shù)進行標定。

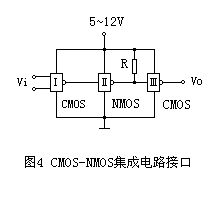

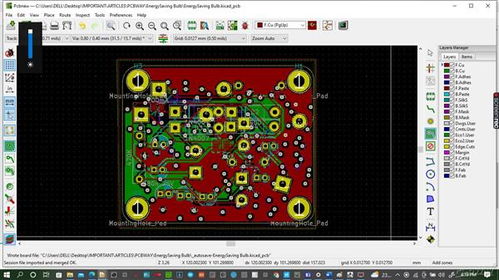

- 抗干擾設(shè)計:在轉(zhuǎn)換電路輸入端采用屏蔽和驅(qū)動保護,PCB布局時模擬與數(shù)字地線分開,最后單點連接,以減少噪聲。

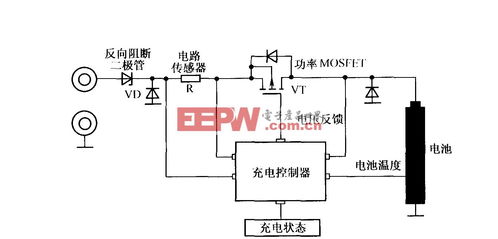

- 電源穩(wěn)定性:為模擬轉(zhuǎn)換部分提供穩(wěn)定、低噪聲的供電,關(guān)鍵部位可增加LC濾波或使用線性穩(wěn)壓器。

設(shè)計一個性能穩(wěn)定的三位數(shù)字電容表,關(guān)鍵在于構(gòu)建一個線性度好、穩(wěn)定性高的電容-時間轉(zhuǎn)換前端,并配以精準的時基和控制邏輯。采用CD4553、CD4511等經(jīng)典數(shù)字集成電路可以構(gòu)建出結(jié)構(gòu)清晰、成本可控的系統(tǒng)。對于更高精度的要求,則需考慮使用集成電容數(shù)字轉(zhuǎn)換器(CDC)的方案,將模擬信號處理全部集成于芯片內(nèi)部,從而大幅簡化外圍電路設(shè)計并提升整體性能。

如若轉(zhuǎn)載,請注明出處:http://www.szseu.org.cn/product/47.html

更新時間:2026-03-23 14:29:54